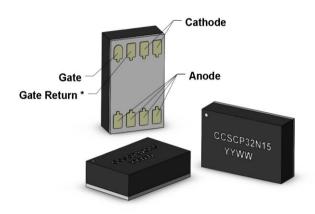

The **CCSCP32N15** is an advanced high-voltage current-controlled thyristor packaged in a **C-Pak SMT package**.

Like all Solidtron products, the internal semiconductor employs high cell density and an advanced planer termination design to achieve high peak current capability, low conduction loss, low off-state leakage, negligible turn-on delay jitter, and most importantly, extremely high turn-on di/dt capability. It is ideally suited for a wide variety of capacitor discharge applications requiring precise timing and rapid energy transfer capability.

The **C-Pak** is a custom surface mount package in which the semiconductor is conventionally attached to a metalized ceramic substrate, wire bonded, and then encapsulated in epoxy. The **C-Pak** is specifically designed to be compliant with IPC 2221A Section 6.3 Electrical Clearance (any elevation).

The **CCSCP32N15** is intended to replace triggered spark gaps of similar voltage and current ratings.

#### **KEY PRODUCT FEATURES**

- 1500V Repetitive Peak Off-State Voltage

- $\cdot V_{GK} = 0V = OFF$

- · 100kA/µSec di/dt Capability

- < 100nSec Turn-On Delay Time</p>

- · 4kA Repetitive Anode Current

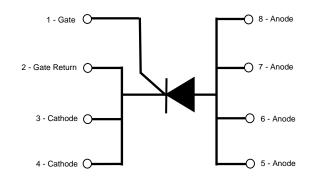

\*The **Gate Return** pad provides a dedicated connection directly to the cathode of the semiconductor die. This connection consists of a single 0.010" aluminum bond wire.

Using the Gate Return pad as an independent gate driver return path reduces V=L\*di/dt induced stress on the gate driver components.

With CCS Solidtron devices, the Gate Return pad may, alternatively, be used as an additional Cathode pad; however, its internal connection possess only 40% of the  $^{\mu}$ T capability of each of the other Cathode pads. Using it in this fashion must be qualified by the customer for their specific application.

#### **MAXIMUM RATINGS**

|                                                                        | VALUE      | UNITS   |

|------------------------------------------------------------------------|------------|---------|

| Peak Off-State Anode Voltage                                           | 1500       | V       |

| Repetitive Peak Forward Anode Current (1/2 Cycle Pulse Width =/<1uSec) | 4000       | А       |

| Repetitive Peak Reverse Anode Current (1/2 Cycle Pulse Width =/<1uSec) | 3500       | А       |

| Critical Off-State Rate of Change of Voltage (dv/dt) immunity          | 5000       | V/uSec  |

| Case Temperature                                                       | -55 to 125 | °C      |

| Rate of Change of Anode Current (di/dt)                                | 100        | kA/uSec |

| Peak Forward Gate Current (=/< 100uSec critically damped pulse)        | 10         | А       |

| Peak Reverse Gate Voltage                                              | -9         | V       |

## **TYPICAL OPERATING CONDITIONS**

|                                                                         | VALUE     | UNITS   |

|-------------------------------------------------------------------------|-----------|---------|

| Off-State Anode Voltage                                                 | 1250      | V       |

| Repetitive Peak Forward Anode Current (1/2 Cycle Pulse Width = 160nSec) | 2700      | A       |

| Repetitive Peak Reverse Anode Current (1/2 Cycle Pulse Width = 160nSec) | 2200      | A       |

| Off-State Rate of Change of Voltage (dv/dt) immunity                    | =/<150    | V/mSec  |

| Case Temperature (Tc)                                                   | -55 to 85 | °C      |

| Rate of Change of Anode Current (di/dt)                                 | 65        | kA/µSec |

| Peak Forward Gate Current (<100uSec)                                    | .5        | A       |

| Peak Reverse Gate Voltage (Incidental)                                  | -5        | V       |

| Repetition Rate                                                         | <1        | Hz      |

### **ELECTRICAL CHARACTERISTICS**

|                                         | CONDITIONS                                   |                                            | VALUES           | UNITS   |

|-----------------------------------------|----------------------------------------------|--------------------------------------------|------------------|---------|

| Anode-Cathode Breakdown Voltage         | Gate shorted to                              | TC = -55 °C                                | 1500             | V       |

|                                         | Cathode, IA=100uA                            | TC = +25 °C                                | Min. 1500        | V       |

|                                         |                                              | TC = +125 °C                               |                  | V       |

|                                         | Gate shorted to                              | TC = -55 °C                                | Max. 50          | nA      |

| Anode-Cathode Off-State Current         | Cathode, VAK=1500V                           | TC = +25 °C                                | Max. 100         | nA      |

|                                         |                                              | TC = +85 °C                                | Max. 1           | μΑ      |

|                                         |                                              | TC = +125 °C                               | Max. 10          | μΑ      |

| Gate Trigger Voltage                    | V <sub>AK</sub> = 12V, I <sub>D</sub> =1mA   | V <sub>AK</sub> = 12V, I <sub>D</sub> =1mA |                  | V       |

| Input Capacitance                       | Bias=6V, Freq. =120Hz                        | Bias=6V, Freq. =120Hz                      |                  | nF      |

| Turn-on Delay Time                      | Capacitor Discharge Through CVR              |                                            | Typ. 50 Max. 100 | nSec    |

| Rate of Change of Anode Current (di/dt) | C=.13uF, LSERIES = 20                        | C=.13uF, LSERIES = 20nH, VSUPPLY = 1250V,  |                  | kA/uSec |

| Peak Anode Current                      | RSERIES=50mohms, TC = $+25$ °C, IG = $0.5$ A |                                            | Typ. 2.7         | kA      |

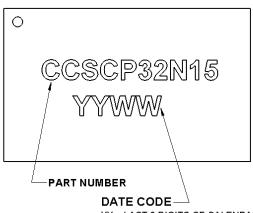

#### **MARKINGS**

YY = LAST 2 DIGITS OF CALENDAR YEAR WW = WORK WEEK OF THE CALENDAR YEAR

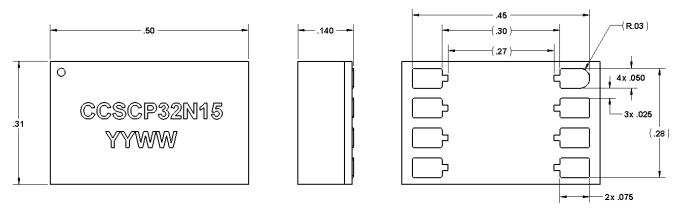

#### **PACKAGING DIMENSIONS**

#### **DIMENSIONS ARE IN INCHES**

TOLERANCES UNLESS OTHERWISE NOTED: TWO PLACE DECIMAL +/-0.010 THREE PLACE DECIMAL +/-0.004

#### **HANDLING AND STORAGE**

# **ESD Sensitivity**

**THIS DEVICE IS ESD SENSITIVE**. OBSERVE PRECAUTIONS FOR HANDLING ELECTROSTATIC DISCHARGE SENSITIVE DEVICES IN ALL ASSEMBLY AND TEST AREAS (REF. JESD625).

IMPROPER HANDLING OF THIS DEVICE MAY PERMANENTLY DAMAGE THE DEVICE AND RENDER IT UNUSABLE.

# **Moisture Sensitivity**

**C-Pak SMD Packages** have not yet been characterized in accordance with recognized MSL standards.

To limit moisture absorption, **C-Pak** products are packed/shipped in a Moisture Barrier Bag (MBB) containing desiccant.

### **Solderability**

The component pads of the **C-Pak**, *although gold plated*, **are subject to oxidation** of the underlying nickel if handled or stored inappropriately. Prolonged exposure to circumstances known to promote nickel oxidation should be avoided; otherwise, solderability of the **C-Pak** will be compromised.

#### **General**

It is highly recommended customers qualify this product with their specific SMD storage, baking and reflow processes, equipment & materials to ensure overall satisfactory installation is achievable.

**CAUTION:** baking of **C-Pak SMD Packages** may cause increased oxidation of the terminations, which if excessive, can result in solderability problems during board assembly. The temperature and time for baking this SMD package should, therefore, be limited with solderability considerations in mind.

Semiconductor Discharge Switch, C-Pak

Datasheet Rev 2 CAO-20170615

### **Legal Notice**

Silicon Power Corporation makes no warranty or guarantee regarding the suitability of this product for any specific application nor does Silicon Power Corporation assume any liability associated with the use of this product. Silicon Power specifically disclaims any and all liability; including without limitation, incidental, consequential or collateral damages incurred while using this product.

Silicon Power Corporation reserves the right to make changes to this product to improve reliability, manufacturability, function or design. Changes may include but are not limited to: materials, material sources, manufacturing processes, manufacturing equipment, parts vendors, service vendors and documentation. Although Silicon Power Corporation will make a reasonable effort to notify customers of changes to this product, notification of changes is not guaranteed.

Parameters and specifications listed within this datasheet will vary in different applications, conditions or environments not specifically addressed. Use of this product within an application must be validated by the customer's technical expert(s).

This product is not designed, intended or authorized for use in applications intended to save or sustain life, specifically those in which the failure of this product could create a situation where personal injury or loss of life may result. Should a customer purchase or use this product for any such unintended and unauthorized application, the customer shall indemnify and hold **Silicon Power Corporation** and its officers, employees, subsidiaries, affiliates and distributors harmless regarding all claims, costs, damages and expenses associated with any claim of personal injury or death associated with unauthorized use even if such a claim alleges **Silicon Power Corporation** was negligent regarding the design or manufacture of this product.

End users of this product shall comply with all applicable DOD, ITAR, EAR, USML laws and regulations.